## **EE Objective Paper II (Set - A)**

- 1. A 2000/200 V, 50 Hz single-phase transformer has an exciting current of 0.5A and a coreloss of 600W. When H.V. side is energized by the rated voltage and frequency, the magnetizing current is

- (A) 0.1A

- (B) 0.2A

- (C) 0.3A

- (D) 0.4A

**Key:** (**D**)

**Exp:**  $I_e = 0.5A; W_0 = 600w$

$$I_{w} = \frac{600}{2000} = 0.3A$$

$$\therefore I_{\rm e}^2 = I_{\rm w}^2 + I_{\rm m}^2 \Longrightarrow I_{\rm m} = \sqrt{I_{\rm e}^2 - I_{\rm w}^2} = \sqrt{(0.5)^2 - (0.3)^2} = 0.4A$$

- 2. A 250 kVA, 11000V/400V and 50 Hz single-phase transformer has 80 turns on the secondary, what is the maximum value of flux?

- (A) 2475 mWb

- (B) 0.2 mWb

- (C) 22.5 mWb

Enaineerina Success

(D) 55.2 mWb

**Key:** (C)

Exp: Maximum flux  $\phi_m = \frac{E_s}{4.44N_s f} = \frac{400}{4.44 \times 80 \times 50} = 22.5 \text{mwb}$

- 3. In a normal operation of 400V, 50 Hz transformer, the total iron loss is 2500W. When the supply voltage and frequency are reduced to 200V and 25 Hz respectively, the corresponding loss is 850W. The eddy-current loss at normal voltage and frequency is

- (A) 400W

- (B) 800W

- (C) 1600W

- (D) 200W

**Key:** (**C**)

**Exp:**  $\frac{V_1}{f_1} = \frac{V_2}{f_2} = 8$

$$\frac{w_e}{f_2} = c$$

$\therefore$  w<sub>e</sub>  $\propto$  kf<sup>2</sup>

when V = 400V, f = 50Hz

$$\frac{w_e}{f_1} = c_1 + f_1 c_2 \Rightarrow \frac{2500}{50} = c_1 + 50c_2$$

...(1)

when V = 200 V; f = 2.5 Hz

$$\frac{\mathbf{w}_{e}}{\mathbf{f}_{2}} = \mathbf{c}_{1} + \mathbf{f}_{2}\mathbf{c}_{2} \Rightarrow \frac{850}{25} = \mathbf{c}_{1} + 25\mathbf{c}_{2} \dots (2)$$

Solving (1) & (2);

$$c_1 = 18$$

;  $c_2 = \frac{16}{25}$

$$\therefore w_e \text{ at } 50 \text{Hz} = \frac{16}{25} \times (50)^2 = 1600 \text{ w}$$

- A magnetic circuit has 150 turns-coil, the cross-sectional area  $5 \times 10^{-4}$  m<sup>2</sup> and the length of 4. the magnetic circuit  $25 \times 10^{-2}$  m. What are the values of magnetic field intensity and relative permeability when the current is 2A and total flux is  $0.3 \times 10^{-3}$  Wb?

- (A) 1200 AT/m and 397.9

- (B) 300 AT/m and  $500 \times 10^{-6}$

(C) 300 AT/m and 397.9

(D) 1200 AT/m and  $500 \times 10^{-6}$

Key: (A)

Exp:

$$H = \frac{NI}{1} = \frac{150 \times 2}{25 \times 10^{-2}} = 1200 \text{ At / mt}$$

$$M_{\rm r} = \frac{\mu}{M_0} = \frac{B}{H\mu_0} = \frac{(\phi / A)}{H\mu_0} = \frac{(0.3 \times 10^{-3} / 5 \times 10^{-4})}{1200 \times 4\pi \times 10^{-7}} = 397.9$$

- A 240 V/120 V, 12 kVA auto-transformer has 96.2% efficiency at full-load and unity power-5. factor. The full-load efficiency at 0.85 pf lagging when connected to a load across 360V would be

- (A) 89.5%

- (B) 92.8% J Ine (C) 98.5% SUC (D) 88.9S

Key:

**Exp:** ATR rating =

$$360 \times 100 \times 10^{-3} = 36$$

KVA

$$\eta = 96.2\% = \frac{1}{1 + \frac{P_L}{P_0}} \Rightarrow \frac{P_L}{P_0} = 0.039 \Rightarrow P_L = 0.039 \times 12 = 0.474 \text{ KN}$$

$$\eta \text{ at } 0.8 \text{ p.f} = \frac{1}{1 + \frac{P_L}{P_{0 \text{ (at } 0.8 \text{ pf})}}} = \frac{1}{1 + \left(\frac{0.474}{36 \times 0.85}\right)} = 98.5\%$$

- 6. The percentage resistance and reactance of a transformer are 2% and 4% respectively. The approximate regulation on full load at 0.8 pf lag is

- (A) 12%

- (B) 8%

- (C) 6%

- (D) 4%

Key: **(D)**

Approximation percentage regulation =  $\% R \cos \phi + \% \sin \phi$ Exp:

$$=2\times0.8+4\times0.6=4\%$$

- A 3-phase transformer has 420 and 36 turns on the primary and secondary windings 7. respectively. The supply voltage is 3300V. The secondary line voltage on no-load when the windings are connected in star-delta is nearly

- (A) 22260V

- (B) 1908V

- (C) 164V

- (D) 490V

Key: **(C)**

**Exp:**

$$v_L = \sqrt{3}V_p(star)$$

$$V_p = \frac{V_L}{\sqrt{3}} = \frac{3300}{\sqrt{3}} = 1905.255V$$

for delta,  $V_{L} = r_{n}$

$$\therefore V_{p_2} = V_{p_1} \left( \frac{N_2}{N_1} \right) = 1905.255 \left( \frac{36}{420} \right) \approx 164V$$

- 8. A 4 kVA transformer has iron-loss of 200W and full load copper loss of 200W. The maximum efficiency at unity power factor will be

- (A) 90.9%

- (B) 85.6%

- (C) 80.6%

- (D) 70.9%

Key:

Exp:

$$\eta_{FL_{cos\phi=1}} = \frac{kVA}{kVA + W_{cu} + W_{i}} = \frac{4000}{4000 + 200 + 200} = 90.9\%$$

- 9. A uniformly distributed windings on the stator has three full-pitched coils, each coil having N turns and each turn carrying a current I. The mmf produced by this winding is

- (A) Sinusoidal in waveform with an amplitude 3 NI

- (B) Sinusoidal in waveform with amplitude  $3\frac{NI}{2}$

- (C) Trapezoidal in waveform with amplitude 3NI

- (D) Trapezoidal in waveform with amplitude  $3\frac{NI}{2}$

Key: **(A)**

Exp: when m/c has more than 3 slots /pole/ph, the steps in the mmt wave are neglected and mmf variation is taken as smooth over these slots and as a consequence, stepped mmf wave changes to trapezoidal mmf wave. The trapezoidal mmf wave amplitude =  $3\frac{\text{N1}}{2}$ .

- 10. In dc machines, the field-flux axis and armature-mmf axis are respectively along

- (A) Direct axis and indirect axis

- (B) Direct axis and inter-polar axis

- (C) Quadrature axis and direct axis

- (D) Quadrature axis and inter-polar axis

Kev: **(B)**

◆ ICP-Intensive Classroom Program ◆ eGATE-Live Internet Based Classes ◆ DLP ◆ TarGATE-All India Test Series

- 11. A shunt motor supplied at 250V runs at 900 rpm and the armature current drawn is 30A. The resistance of the armature circuit is  $0.4\Omega$ . The resistance required in series with the armature to reduce the speed to 600 rpm when the armature current is 20A will be

- (A)  $3.17\Omega$

- (B)  $2.17\Omega$

- (C)  $5.17\Omega$

- (D)  $4.17\Omega$

**Key: (D)**

**Exp:**  $Eb_1 = 250 - 30 \times 0.4 = 238V$

Eb ∝ Nφ

$$\frac{238}{\text{Eb}_2} = \frac{900}{600} \Longrightarrow E_{b2} = 158.667 = 250 - 20 \times R_a$$

$$R_a' = 4.56 = 0.4 + R_{eat}$$

$$R_{\rm ext} = 4.17 \Omega$$

- 12. The internal characteristics of a dc generator is plotted between the

- (A) Field current and voltage generated at no load

- (B) Armature current and voltage generated on load

- (C) Armature current and voltage generated after armature reaction

- (D) Field current and voltage generated on load

**Key:** (C)

**Engineering Success**

- 13. The drawbacks of 'Armature Resistance Control' method of speed control of a dc motor are

- 1. A large amount of power is lost in the external resistance R

- 2. This method gives the speed below normal values

- 3. For a specified value of R, speed reduction is not constant. It varies with motor load Which of the above statements are correct?

- (A) 1, 2 and 3

- (B) 1 and 2 only

- (C) 1 and 3 only

- (D) 2 and 3 only

Key: (A)

- 14. A dc motor running at 2000 rpm has a hysteresis loss of 500W and eddy-current loss of 200W. The flux is maintained constant but the speed is reduced to 1000 rpm. At the reduced speed the total iron-loss would be

- (A) 500W

- (B) 400W

- (C) 300W

- (D) 200W

**Key:** (C)

**Exp:**  $W_n \propto f \propto N$ ;  $W_e \propto f^2 \propto N^2$

$$\frac{w_{h_1}}{w_{h_2}} = \frac{2000}{1000} \Rightarrow w_{h_2} = \frac{500}{2} = 250w$$

$$w_{e_2} = w_{e_1}(2)^2 = 200 / 4 = 50w$$

$$\vdots w_i = w_{e_2} + w_{h_2} = 300 w$$

- 15. The speed control of dc shunt motor in both directions can be obtained by

- (A) Armature resistance control method

- (B) Ward Leonard method

- (C) Field diverter method

- (D) Armature voltage control method

Key: (B)

- 16. A 10 hp, 240V dc shunt motor, having armature-circuit resistance of  $0.5\Omega$  and a full-load current of 40A, is started by a starter, such that sections of required resistances in series with the armature circuit should limit the starting current to 150% of the full-load current. The steady-state emf developed by the machine at full-load when the arm of the starter is moved to the next step is

- (A) 120V

- (B) 100V

- (C) 80V

- (D) 60V

**Key:** (C)

**Exp:**  $I_{a} = 40A$

rest at starting =  $r_1 + r_2 + ... + r_n$

- 17. A synchronous motor operates at rated voltage and frequency and has a load torque angle of 30°. If both the terminal voltage and frequency are reduced by 10%, then

- (A) The load torque angle remains the same

- (B) The load torque angle increases

- (C) The load torque angle decreases

- (D) Nothing can be said about the torque angle

**Key:** (A)

**Exp:**  $P = \frac{Ev}{X_a} \sin \delta$

$$P \propto \left(\frac{V^2}{f}\right) \sin \delta \ 0$$

$$T = \frac{P}{\omega_s}; T \propto \left(\frac{V^2}{f^2}\right) \sin \delta$$

: if V and f decreased by same amounts

$\delta$  is constant

- 18. The nature of armature mmf of a zero power factor lagging load in a 3-phase alternator is

- (A) Magnetizing

- (B) De-magnetizing (C) Neutral

- (D) Cross-magnetizing

Key: **(B)**

- 19. The flux/pole in a synchronous motor with stator not connected to supply is  $\phi_1$  and when connected to supply it is  $\frac{3}{4}\phi_1$ . The no-load current drawn from the supply under this condition would be

- (A) Lagging the supply voltage

- (B) Leading the supply voltage

- (C) In phase with the supply voltage

(D) Zero

**Key:**

Exp:

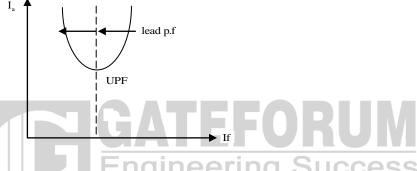

In lag pf region Ia decreases with increase If.

- 20. A cylindrical-rotor generator with internal voltage 2.0 pu and  $X_s = 1.0$  pu is connected by a line of reactance 0.5 pu to a round-rotor synchronous motor of synchronous reactance 1.2 pu and excitation voltage 1.35 pu. When 0.5 pu power is supplied by the generator, the electrical angular difference between the rotors would be

- (A)  $25^{\circ}$

$I_a \propto \phi$

- (B) 30°

- (C)  $60^{\circ}$

- (D) 120°

Key: **(B)**

$P = \frac{Ev}{Xs} \sin \delta$ Exp:

$0.5 = \frac{2 \times 1.35}{(1 + 0.5 + 1.2)} \sin \delta$

$\delta = 30$

- The synchronizing power for one mechanical degree of displacement for a 3-phase, 20000 21. kVA, 6600 V, 50Hz, 12-pole machine having  $X_s = 1.65\Omega$  and negligible resistance is

- (A) 1024.6 kW

- (B) 921.9 kW

- (C) 782.36 kW

- (C) 1182.6 kW

**Exp:**

$$P_{\text{synch}} = \left[ \frac{3V_p Ef}{Xs} \cos \delta \right] \frac{p.\pi}{180}$$

$$= \frac{3 \times \frac{6600}{\sqrt{3}} \times \frac{6600}{\sqrt{3}} \times \cos 0}{1.65} \left(\frac{12}{2}\right) \cdot \frac{\pi}{180}$$

- = 2764.6kw

- =921.53kw per phase

- 22. For obtaining very quick braking of a 3-phase, wound-rotor induction motor running on load

- (A) A large external resistance has to be inserted in the rotor-circuit

- (B) A large external resistance has to be inserted in the stator-circuit

- (C) Interchange any two terminals of the stator supply

- (D) Interchange any two terminals of the rotor to the slip-rings

**Key:** (C)

23. Consider the following statements:

As a three-phase induction motor is loaded from no-load to rated load,

- 1. There is an improvement in the power factor

- 2. The torque increases almost in proportion to slip

- 3. The air-gap flux falls sharply

Which of the above statements are correct?

- (A) 1, 2 and 3

- (B) 1 and 2 only

- (C) 1 and 3 only

- (D) 2 and 3 only

**Key:** (B)

- 24. A small 3-phase induction motor has a short-circuit current 5 times of full-load current and full-load slip 5%. If starting resistance starter is used to reduce the impressed voltage to 60% of normal voltage, the starting torque obtained in terms of full load torque would be

- (A) 30%

- (B) 45%

- (C) 55%

- (D) 80%

Key: (B)

**Exp:**

$$\frac{T_{st}}{T_{f_1}} = k^2 \left(\frac{I_{sc}}{I_{fL}}\right)^2 \times s_H = (0.6)^2 \times \left(\frac{5}{1}\right)^2 \times 0.05 = 45\%$$

- 25. The frequency of rotor emf of an 8-pole induction motor is 2 Hz. If the supply frequency is 50 Hz, then the motor speed is

- (A) 1500 rpm

- (B) 750 rpm

- (C) 375 rpm

- (D) 720 rpm

**Key: (D)**

**Exp:**

$$N_s = \frac{120f}{p} = \frac{120 \times 50}{8} = 750 \text{ rpm}$$

$$s = \frac{N_s - N}{N_s} \Rightarrow \frac{2}{50} = \frac{750 - N}{750} \Rightarrow N = 720 \text{ rpm}$$

- 26. For a given applied voltage and current, the speed of a universal motor will be

- (A) Higher in dc excitation than in ac excitation

- (B) Higher in ac excitation than in dc excitation

- (C) Same in both dc and ac excitations

- (D) Dangerously high in dc excitation

Key: (A)

Exp:

For an universal motor, speed with DC excitation is higher than with AC.

- 27. Two single-phase transformers A and B with equal turn's ratio have reactances of  $j3\Omega$  and  $j9\Omega$  referred to secondary. When operated in parallel, the load-sharing of 100 kW at 0.8 pf lag between A and B transformers would respectively be

- (A) 75 kW and 25 kW

(B) 60 kW and 40 kW

(C) 20 kW and 80 kW

(D) 25 kW and 80 kW

**Key:** (D)

**Exp:**

$$P_A = P. \frac{X_A}{X_A + X_B} = 100. \frac{j_3}{j_3 + j9} = 25 \text{kw}$$

$$P_{\rm B} = P.\frac{X_{\rm B}}{X_{\rm A} + X_{\rm B}} = 100 \frac{j9}{j3 + j9} = 75 \text{kw}$$

- 28. Compared to turbines in the conventional coal-fired thermal stations, nuclear power plant turbines use steam at

- (A) Higher pressure and higher temperature (B) Lower pressure and lower temperature

- (C) Higher pressure and lower temperature (D) Lower pressure and higher temperature

- 29. In an L-section filter, a bleeder resistance connected across the load

- (A) Provides good regulation for all values of load

- (B) Ensures lower PIV of the diodes

- (C) Ensures lower values of capacitance in the filter

- (D) Reduces ripple content

**Key: (D)**

- 30. The power output from a hydro-electric power plant depends on

- (A) Head, type of dam and discharge

- (B) Head, discharge and efficiency of the system

- (C) Type of draft tube, type of turbine and efficiency of the system

- (D) Type of dam, discharge and type of catchment area

**Key: (B)**

31. Incremental fuel costs of two units A and B of a power station are

$$\frac{\mathrm{dF_A}}{\mathrm{dP_A}} = 0.4\,\mathrm{P_A} + 400$$

$$\frac{dF_{\rm B}}{dP_{\rm B}} = 0.48\,P_{\rm B} + 320$$

**GATEFORUM**

For the minimum cost of generation of a total load of 900 MW, the generation allocation for A and B units respectively are

(A) 200MW and 700 MW

- (B) 300 MW and 600 MW

- (C) 400 MW and 500 MW

- (D) 500 MW and 400 MW

**Kev:** (**C**)

Exp:

$$\frac{dl}{dt}$$

$$\frac{dF_A}{dP_A} = \frac{dF_B}{dP_B} \Longrightarrow 0.4P_A - 0.48P_B = -80$$

Given,

$$P_{A} + P_{B} = 900$$

Solving (1) & (2),  $P_A = 400 \text{Mw} \& P_B = 500 \text{mW}$

- 32. A power station has a maximum demand of 2500 kW and number of kWh generated per year is  $45 \times 10^5$ . The load factor is

- (A) 10.25%

- (B) 20.5%

- (C) 41%

- (D) 82%

**Exp:** Load factor =

$$\frac{\text{kwh / per hour}}{\text{max. demand}} = \frac{45 \times 10^5 / 365 / 24}{2500} = 20.5\%$$

- 33. A long overhead lossless power transmission line is terminated with its characteristics impedance. While the line is in operation

- (A) A resonance of reactive powers occurs in the line

- (B) The line becomes purely inductive

- (C) The line becomes purely capacitive

- (D) There is no reflected wave on the line

**Key:** (**D**)

- 34. For exact compensation of voltage drop in the feeder, the booster must

- (A) Be earthed

- (B) Work on line voltage

- (C) Work on its linear portion of V-I characteristics

- (D) Work on its non-linear portion of V-I characteristics

- **Key:** (C)

- **Exp:** A booster is a dc generator whose function is to inject or add certain voltage into a circuit so as to compensate the IR drop in the feeder etc. For exact compensation, the booster must be marked on the straight or linear portion of its V-I characteristics

- 35. A 100 MVA, 50 Hz turbo-generator operates at no load at 3000 rpm. A load of 25 MW is suddenly applied to the machine and the steam valve to the turbine commences to open after 0.6 seconds due to the governor time-lag. Assuming the inertia constant H = 5.0 kW-s per kVA of the generator rating, the frequency to which the generator voltage drops before the steam-flow commences to meet the new load is

- (A) 49.0 Hz

- (B) 50.15 Hz

- (C) 49.24 Hz

- (D) 49.82 Hz

**Key:** (C)

Exp:

$$H = \frac{\text{stored Energy}}{\text{capacity of m/c}}$$

The energy stored at no load  $= 5 \times 100 = 500 \text{mJ}$

Before the steam values open the energy lost by the rotor

$$=25\times0.6=15 \,\text{MJ}$$

$$f_{\text{new}} = \sqrt{\frac{500 - 15}{500}} \times 50 = 49.24 \text{ Hz}$$

- 36. In case of single line to ground fault

- (A) All sequence networks are connected in parallel

- (B) All sequence networks are connected in series

- (C) Positive and negative sequence networks are connected in parallel

- (D) Zero and negative sequence networks are connected in series

| 37. | What is the region of operation of a 3-phase inverter employing sinusoidal PWM when the |

|-----|-----------------------------------------------------------------------------------------|

|     | peak-to-peak values of both the carrier and the modulating waves are made equal?        |

(A) Linear modulation

(B) Over modulation

- (C) Boundary of linear modulation and over modulation

- (D) Six-step operation

**Key: (D)**

38. Which of the following circuit breakers has the lowest voltage range?

(A) SF<sub>6</sub> circuit breaker

(B) Air-blast circuit breaker

(C) Tank type oil circuit breaker

(D) Air-break circuit breaker

Key: (D)

**Exp:** Air break CB's are available in the voltage range 400 to 12KV.

- 39. Which of the following will be provided to reduce the harmonics on the ac side of an HVDC transmission line?

- (A) Synchronous motors in over excited condition

(B) Shunt capacitor

(C) Static compensator

(D) Shunt filters

GATEFORUM Engineering Success

**Key: (D)**

40. Modified McMurray full-bridge inverter works on

(A) Voltage commutation

(B) Current commutation

(C) Load commutation

(D) Complementary commutation

Key: (A)

- 41. When a PNP transistor is properly biased, the holes from the emitter

- (A) Diffuse through the base into the collector region

- (B) Recombine with the electrons in the base region

- (C) Recombine with the electrons in the emitter region

- (D) Diffuse through the emitter to collector

Key: (A)

- 42. In a P-N junction diode under reverse bias, the magnitude of electric field is maximum at

- (A) The edge of the depletion region on the P side

- (B) The edge of the depletion region on the N side

- (C) The centre of the depletion region on the N side

- (D) The P-N junction

**Key: (D)**

- 43. A silicon diode is preferred to a germanium diode because of its

- (A) Higher reverse current

- (B) Lower reverse current and higher reverse break down voltage

- (C) Higher reverse current and lower reverse break down voltage

- (D) None of the above

Key: **(B)**

- 44. Compared to an ordinary semiconductor diode, a Schottky diode has

- (A) Higher reverse saturation current and zero cut-in voltage

- (B) Higher reverse saturation current and higher cut-in voltage

- (C) Higher reverse saturation current and lower cut-in voltage

- (D) Lower reverse saturation current and lower cut-in voltage

Key: **(C)**

- 45. Which of the following is called 'hot carrier diode'?

- (A) PIN diode

- (B) LED

- (C) Photo diode

- (D) Schottky diode

Key: **(D)**

In a voltage-series-feedback amplifier with open loop gain A<sub>v</sub> and the feedback factor β, the 46. input resistance becomes Engineering Success

$$(A) \frac{R_{j}}{\left(1 + \beta A_{v}\right)}$$

(A)  $\frac{R_{j}}{(1+\beta A_{v})}$  (B)  $R_{i}\sqrt{(1+\beta A_{v})}$  (C)  $R_{i}(1+\beta A_{v})$  (D)  $\frac{R_{i}}{\sqrt{(1+\beta A_{v})}}$

Key: **(C)**

- 47. Ripple-rejection ratio of voltage regulator is the ratio of

- (A) Output voltage to input ripple voltage

- (B) Output power to input power of regulator

- (C) Input power to output power of regulator

- (D) Input ripple voltage to output ripple voltage

Key: **(D)**

- 48. Variation in  $\beta$  in a BJT can cause a fixed bias circuit to so

- (A) Into active mode of operation from saturation mode

- (B) Out of active mode

- (C) Out of saturation

- (D) Into cutoff mode from active mode of operation

- 49. In a McMurray inverter, diodes are connected in inverse parallel to thyristors to

- (A) Protect the thyristor

- (B) Make the turn off of the thyristor successful

- (C) Make the turn on of the thyristor successful

- (D) Provide path to the reactive component of the load current

Which of the above statements are correct?

- (A) 1 and 3

- (B) 1 and 4

- (C) 2 and 4

- (D) 2 and 3

**Key:** (C)

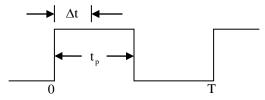

50. Following pulse is applied to an SR flip flop.

If  $\Delta t$  is propagation delay, which of the following relations should hold to avoid the race condition?

- (A)  $t_p < \Delta t < T$

- (B)  $\Delta t < t_p < T$

- (C)  $2\Delta t < t_p$

- (D)  $2\Delta t < t_p < T$

Key: (A)

Exp: Race around condition can be avoided by three ways:-

- 1. Edge triggering of flip-flop.

- 2. master-slave flip-flop

- 3.  $\Delta t < t_p < T$

- 51. For a four variable K-Map, if each cell is assigned one integer value in range 0-15 then which is the cells adjacent to the cell corresponding to decimal value 7?

- (A) 3, 5, 6 and 8

- (B) 3, 5, 10 and 11

- (C)3, 5, 6 and 15

- (D) 4, 6, 8 and 15

**Key:** (C)

Exp:

| AB       | 00 | 01 11 | 10 |    |

|----------|----|-------|----|----|

| 00       | 0  | 1     | 3  | 2  |

| 01<br>11 | 4  | 5     | 7  | 6  |

| 10       | 12 | 13    | 15 | 14 |

|          | 8  | 9     | 11 | 10 |

Any two cells can be called adjacent to each other if one and only one-bit is changing. So, cell no. 7 is adjacent to cell no. 3, 5, 6 and 15.

- 52. In order to generate a square wave from a sinusoidal input signal, one can use

- 1. Schmitt trigger circuit

- 2. Clippers and amplifiers

- 3. Monostable multivibrator

Which of the above statements are correct? Ening Success

- (A) 1, 2 and 3

- (B) 1 and 2 only (C) 1 and 3 only (D) 2 and 3 only

Key: **(C)**

- 53. An analog voltage in the range of 0-8V is divided in eight equal intervals for conversion to 3bit digital output. The maximum quantization error is

- (A) 0V

- (B) 0.5V

- (C) 1.0V

- (D) 2.0V

Key: **(B)**

Maximum quantization error  $=\pm\frac{\Delta}{2}=\pm\frac{1}{2}$  volt  $=\pm0.5$ V

Where  $\Delta = \text{Re solution}$

$$\Delta = \frac{V_{max}}{2^n} = \frac{8}{2^3} = 1$$

- 54. The logic function A+BC is the simplified form of which of the following?

- (A) AB+BC

- (C)  $\overline{AB} + A\overline{BC}$

- $(C) \overline{ABC}$

- (D) (A+B)(A+C)

Key: **(D)**

As per the transposition theorem Exp:

$$A + BC = (A + B).(A + C)$$

- 55. Program counter in a digital computer

- (A) Counts the numbers of programs run in the machine

- (B) Counts the number of times a subroutine is called

- (C) Counts the number of times the loops are executed

- (D) Points the memory address of the current or the next instruction to be executed

Key: **(D)**

Exp: Program counter in a digital computer points the memory address of the current or the next instruction (or byte) to be executed.

- 56. Each cell of a static RAM contains

- (A) 4 MOS transistors

(B) 4 MOS transistors and 1 capacitor

(C) 2 MOS transistors

(D) 4 MOS transistors and 2 capacitors

Key: **(A)**

Exp: SRAM contains 4 MOS transistors.

- 57. If an npn silicon transistor is operated at  $V_{CE} = 5V$  and  $I_{C} = 100 \mu A$  and has a current gain of 100 in the CE connection, then the input resistance of this circuit will be

- (A)  $250k\Omega$

- (B)  $450k\Omega$

- (C)  $4500 \text{k}\Omega$

- (D)  $2500 \text{k}\Omega$

Key:

$$\beta = 100$$

$$(25k \text{ ohm})$$

$$\beta = 100$$

Engineering Success

$$R_{in} = (\beta \pi) \frac{V_T}{I_E} = \frac{(\beta + 1) V_T}{I_C} . \alpha : V_T = 25 \text{ mV}$$

$$= \frac{\beta V_T}{I_C} = 100 \times \frac{25 \times 10^{-3}}{100 \times 10^{-6}}$$

$$= 25 \text{ k}\Omega$$

- 58. A 4-bit synchronous counter has flip-flops having propagation delay of 50 ns each and AND gates having propagation delay of 20 ns each. The maximum frequency of clock pulses can be

- (A) 20 MHz

- (B) 50 MHz

- (C) 14.3 MHz

- (D) 5 MHz

Key:

Exp:

$$f_{\text{max}} = \frac{1}{t_{\text{pd}} + t_{\text{And}}} = \frac{1}{(50 + 20)10^{-9}}$$

=14.28 MHz

- 59. A self-starting counter is one that can start

- (A) The sequence from initial count and continues its sequence

- (B) The sequence from any state among the sequence and continues its normal count sequence

- (C) From any state but eventually reaches the required count sequence

- (D) None of the above

**Key:** (C)

- 60. When a program is being executed in an 8085 microprocessor, its program counter contains

- (A) The memory address as the instruction that is to be executed next

- (B) The memory address of the instruction that is being currently matched

- (C) The total number of instructions in the program being executed

- (D) The number of instructions in the current program that have already been executed

Key: (A)

**Exp:** In 8085 microprocessor, its program counter contains the memory address as the instruction that is to be executed next.

- 61. A 'DADH' instruction is the same as shifting each bit by one position to the

- (A) Left

- (B) Right

- (C) Left with a zero inserted in LSB position

- (D) Right with a zero inserted in LSB position

**Key:** (C)

Exp: DAD H→ instruction will perform right with a zero inserted in LSB position. This can be checked by taking any values of HL.

- 62. Which one of the following statements is correct about 8086?

- (A) It is 46 PM IC and uses 5V dc supply

- (B) It uses 20 lines for data bus

- (C) It multiplexes status signals with address bus

- (D) It is manufactured using CMOS technology

**Key:** ()

- 63. During which T-state, contents of OP code from memory are loaded into IR (Instruction Register)?

- (A) T<sub>1</sub> OP code Fetch

(B) T<sub>2</sub> OP code Fetch

(C) T<sub>3</sub> OP code Fetch

(D) T<sub>4</sub> OP code Fetch

Key: (A)

**Exp:** Reading of the data from memory will start second state (T2) and will finish within T<sub>3</sub> state of opcode fetch operation.

| 64.         | In 8085 microprocessor, the address for 'TRAP' interrupt is                                                                                   |                          |                          |                              |  |  |  |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|--------------------------|------------------------------|--|--|--|

|             | (A) 0024 H                                                                                                                                    | (B) 002 CH               | (C) 0034 H               | (D) 003 CH                   |  |  |  |

| Key:        | $(A) \\ 4.5 \times 8 = 36 = 0024.$                                                                                                            | Н                        |                          |                              |  |  |  |

| 65.         | Assuming LSB is at position 0 and MSB at position 7, which bit positions are not used (undefined) in Flag Register of an 8085 microprocessor? |                          |                          |                              |  |  |  |

|             | (A) 1, 3, 5                                                                                                                                   | (B) $2, 3, 5$            | (C) 1, 2, 5              | (D) 1, 3, 4                  |  |  |  |

| Key:        | <b>(A)</b>                                                                                                                                    |                          |                          |                              |  |  |  |

| Exp:        | Flags in 8085                                                                                                                                 |                          |                          |                              |  |  |  |

|             | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                         |                          |                          |                              |  |  |  |

|             | Dit position 1, 3 and                                                                                                                         | s are not defined.       |                          |                              |  |  |  |

| 66.         | At the beginning of a                                                                                                                         | a fetch cycle, the conte | nts of the program coun  | ter are                      |  |  |  |

| 00.         | (A) Incremented by                                                                                                                            | •                        | (B) Transferred to add   |                              |  |  |  |

|             |                                                                                                                                               |                          | rs (D) Transferred to me |                              |  |  |  |

| Key:        | (A)                                                                                                                                           |                          |                          |                              |  |  |  |

| - 0         |                                                                                                                                               | Engine                   | ering Sug                | ccess                        |  |  |  |

| 67.         | What will be the confollowing instruction                                                                                                     | ntents of DE and HL re   |                          | y after the execution of the |  |  |  |

|             | LXIH, 2500H                                                                                                                                   |                          |                          |                              |  |  |  |

|             | LXID, 0200H                                                                                                                                   |                          |                          |                              |  |  |  |

|             | DAD D                                                                                                                                         |                          |                          |                              |  |  |  |

|             | XCHG                                                                                                                                          |                          |                          |                              |  |  |  |

|             | (A) 0200H, 2500H                                                                                                                              | (B) 0200H, 2700H         | (C) 2500H, 0200H         | (D) 2700H, 0200H             |  |  |  |

| <b>Key:</b> | <b>(D)</b>                                                                                                                                    |                          |                          |                              |  |  |  |

| Exp:        | LXI H, 2500H $\rightarrow$ H                                                                                                                  | 25 00H L                 |                          |                              |  |  |  |

|             | LXI D,0200H $\rightarrow$ D 02 00H E                                                                                                          |                          |                          |                              |  |  |  |

|             | $DAD D \rightarrow HL + DE = 2500H + 0200H = H  27  00H  L$                                                                                   |                          |                          |                              |  |  |  |

|             | XCHG → Exchange the content of the HL pair with DE register pair.                                                                             |                          |                          |                              |  |  |  |

|             | $DE \rightarrow 2700H$                                                                                                                        |                          |                          |                              |  |  |  |

|             | $GL \rightarrow 0200H$                                                                                                                        |                          |                          |                              |  |  |  |

|             |                                                                                                                                               |                          |                          |                              |  |  |  |

|             |                                                                                                                                               |                          |                          |                              |  |  |  |

- 68. Direction flag is used with

- (A) String instructions

- (B) Stack instructions

- (C) Arithmetic instructions

- (D) Branch instructions

Key: (A)

The **direction flag** is a flag that controls the left-to-right or right-to-left direction of string processing

- 69. XCHG instruction of 8085 exchanges the content of

- (A) Top of stack with contents of register pair

- (B) BC and DE register pairs

- (C) HL and DE register pairs

- (D) None of the above

**Key:** (C)

**Exp:**  $XCHG \rightarrow Exchange the content of HL with DE registers pair.$

- 70. To interface a slow memory, wait states are added by

- (A) Extending the time of the chip select logic

- (B) Causing READY signal to go low

- (C) Causing READY signal to go high

- (D) By increasing the clock frequency

Key: (C)

**Exp:** Wait states can be increased by keeping the READY signal HIGH.

- 71. A ripple counter with n flip-flops can function as a

- (A) n:1 counter

- (B)  $\frac{n}{2}$ :1 counter

- (C)2n:1 counter

- (D) 2<sup>n</sup>:1 counter

**Key: (D)**

**Exp:** A ripple counter with n flip-flop will generate  $2^n$  states in one cycle, so it is called as  $2^n : 1$  counter.

- 72. The relation among IC (Instruction Cycle), FC (Fetch Cycle) and EC (Execute Cycle) is

- (A) IC = FC-EC

- (B) IC = FC + EC

- (C) IC = FC + 2EC

- (D) EC = IC + FC

**Key: (B)**

**Exp:** Instruction cycle is defined as the sum of fetch cycle and execution cycle i.e

IC = FC + EC

| 73.                | Each instruction in an assembly language program has the following fields.                                                                                                                                                                                                                                         |                          |                     |                       |  |  |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|---------------------|-----------------------|--|--|

|                    | (A) Label field                                                                                                                                                                                                                                                                                                    | (B) Mnemonic field       | d (C) Operand field | (D) Comment field     |  |  |

|                    | What is the correct sequence of these fields?                                                                                                                                                                                                                                                                      |                          |                     |                       |  |  |

|                    | (A) 1, 2, 3 and 4                                                                                                                                                                                                                                                                                                  | (B) 2, 1, 4 and 3        | (C) 1, 3, 2 and 4   | (D) 2, 4, 1 and 3     |  |  |

| Key:               | <b>(A)</b>                                                                                                                                                                                                                                                                                                         |                          |                     |                       |  |  |

| 74.                | A memory system has a total of 8 memory chips, each with 12 address lines and 4 data lines. The total size of the memory system is                                                                                                                                                                                 |                          |                     |                       |  |  |

|                    | (A) 32 k bytes                                                                                                                                                                                                                                                                                                     | (B) 48 k bytes           | (C) 64 k bytes      | (D) 6k bytes          |  |  |

| Key:               | ( )                                                                                                                                                                                                                                                                                                                |                          |                     |                       |  |  |

| 75.                | Among the given instructions, the one which affects maximum number of flags is                                                                                                                                                                                                                                     |                          |                     |                       |  |  |

| Voru               | (A) RAL                                                                                                                                                                                                                                                                                                            | (B) POP PSW              | (C) XRA A           | (D) DCR A             |  |  |

| Key:               |                                                                                                                                                                                                                                                                                                                    |                          |                     |                       |  |  |

| Exp:               | AKA A Instruction                                                                                                                                                                                                                                                                                                  | will affect maximum i    | lumber of mags.     |                       |  |  |

| 76.<br><b>Key:</b> | The internal characteristics of a dc generator is plotted between the  (A) Armature current and voltage generated after armature reaction  (B) Field current and voltage generated at no load  (C) Field current and voltage generated on load  (D) Armature current and voltage generated at the output terminals |                          |                     |                       |  |  |

| Kty.               | (A)                                                                                                                                                                                                                                                                                                                |                          |                     |                       |  |  |

| 77.                | In 8085 microprocessor with memory mapped I/O, which one of the following is correct?  (A) I/O devices have 16 bit addresses  (B) I/O devices are accessed during IN and OUT instructions  (C) There can be a maximum of 256 input and 256 output devices  (D) Logic operations cannot be performed                |                          |                     |                       |  |  |

| Key:               | (A)                                                                                                                                                                                                                                                                                                                | is camot be performed    | •                   |                       |  |  |

| Exp:               | In memory mapped I/O in 8085, all the address lines of memory is used as a address lines of I/O ports.                                                                                                                                                                                                             |                          |                     |                       |  |  |

| 78.                | Race-around condition occurs in                                                                                                                                                                                                                                                                                    |                          |                     |                       |  |  |

|                    | (A) Multiplexer                                                                                                                                                                                                                                                                                                    | (B) ROM                  | (C) Flip-flops      | (D) Voltage regulator |  |  |

| Key:               | (C)                                                                                                                                                                                                                                                                                                                |                          |                     |                       |  |  |

| Exp:               | Race-around condit                                                                                                                                                                                                                                                                                                 | tion occurs in Flip-flop | S                   |                       |  |  |

|                    |                                                                                                                                                                                                                                                                                                                    |                          |                     |                       |  |  |

- 79. The DMA transfer technique where one word data is transferred at a time is called

- (A) Cycle stealing

- (B) Memory stealing

- (C) Hand shaking

- (D) Interleaving

Key: (A)

- 80. In a single-phase to single-phase cyclo-converter, the magnitudes of harmonic components are quite large. How can they are reduced?

- (A) By using a chopper circuit

- (B) By using an RC oscillator

- (C) By using a three phase input supply

- (D) By adding an alternator to the input

**Key:** (**D**)

- 81. Which one of the following is used for serial I/O transfer in 8085 based system?

- (A) 8251

- (B) 8255

- (C) 8259

- (D) 8279

**Key:** (B)

Exp: 8255 IC is used for serial I/O transfer

82. An analog voltage is in the range of 0 to 8V. It is divided in 8 equal intervals for conversion to 3-bit digital output. The maximum quantization error is

naineerina

- (A) 0V

- (B) 0.5V

- (C) 1V

- (D) 2V

**Key: (B)**

**Exp:**

$$\Delta = \frac{8}{8} = 1$$

Maximum quantization errors are

$$\frac{\Delta}{2} = \frac{1}{2} = 0.5$$

- 83. Digital modulation techniques are used in satellite communication system, because

- (A) They are easier to handle

- (B) Large bandwidth utilization is possible

- (C) They have a spectral efficiency

- (D) They are less prone to interference

**Key: (D)**

- 84. In FM modulation, when the modulation index increases, the transmitted power is

- (A) Increased

- (B) Decreased

- (C) Unchanged

- (D) Not related

**Key:** (C)

**Exp:** In FM, transmitted power is

$$P_{t} = \frac{A_{c}^{2}}{2}$$

Means, it does not depend on modulation index.

- 85. In TV, Video signals are transmitted through

- (A) Amplitude modulation

- (B) Frequency modulation

- (C) Either amplitude or frequency modulation

- (D) Neither amplitude nor frequency modulation

**Key:** (**D**)

**Exp:** In Television transmitters uses both AM and FM, the video (or) picture signals are transmitted by AM and the sound by FM.

- 86. If the number of bits per sample in a PCM system is increased from 8 to 16, then the bandwidth will be increased by

- (A) 2 times

- (B) 4 times

- (C) 8 times

- (D) 16 times

Key: (C)

**Exp:** Bandwidth  $\alpha$  n

$$\frac{\mathbf{B}_1}{\mathbf{B}_2} = \frac{\mathbf{n}_1}{\mathbf{n}_2}$$

$\mathbf{B}_2 = 2\mathbf{B}_1$

- 87. In a PCM system, a five bit-encoder is used. If the difference between two consecutive levels is 1V, then the range of the encoder is

- (A) 0-31V

- (B) 0-30V

- (C) 1-32V

- (D) 1-30V

**Key:** (A)

- 88. Consider the following types of modulation:

- 1. Amplitude modulation

- 2. Frequency modulation

- 3. Pulse modulation

- 4. Pulse modulation

Which of the above modulation are used for telecasting TV programs?

- (A) 2 and 3

- (B) 3 and 4

- (C) 1 and 2

- (D) 1 and 4

**Key:** (A)

**Exp:** Television transmitters uses both AM and FM.

- (1) The video (or) picture signals are transmitted by AM

- (2) and sound signal by FM

- 89. In a step up operation, what is the condition to be satisfied for controllable power transfer?

- (A)  $0 < V_S < E$

- (B)  $0 < V_S > E$

- (C)  $V_s < E$

- (D)  $V_S > E$

Key: (A)

**Exp:** To make the system stable i.e., to stop rising of inductor current, the conditions for controllable power transfer are a

$0 < V_{s} < E$ .

- 90. A Schottky diode is

- (A) A majority carrier device

- (B) A minority carrier device

- (C) A fast recovery diode

- (D) Both majority and minority carrier diode

**Key:** (A)

91. An SCR has  $V_{DRM} = 600V$ ,  $\left(\frac{dv}{dt}\right)_{max} = 25V/\mu s$ , and  $\left(\frac{di}{dt}\right)_{max} = 30A/\mu s$ . It is used to energize a

$100\Omega$  resistance load. What are the minimum values for an RC snubber circuit to avoid unintentional triggering? (V<sub>DRM</sub> means peak repetitive forward blocking voltage)

(A)

$$T = 10 \mu s$$

,  $C = 2.4 \mu F$  and  $R = 4.5 m\Omega$

(B)

$$T = 24 \mu s$$

,  $C = 0.24 \mu F$  and  $R = 4.5 \text{ m}\Omega$

(C)

$$T = 24 \mu s$$

,  $C = 2.4 \mu F$  and  $R = 7.0 \text{ m}\Omega$

(D)

$$T = 10\mu s$$

,  $C = 0.24 \mu F$  and  $R = 7.0 \text{ m}\Omega$

**Key:** (C)

Exp:

$$C_s \ge \frac{V_1}{R_L \frac{dv}{dt}} \Rightarrow C_s \ge \frac{600}{10 \times 25} \Rightarrow C_s \ge 2.4 \text{MF}$$

$$T = \frac{600}{25} = 24 Ms$$

- 92. Maximum string efficiency is achieved when

- (A) Uniform distribution of voltage across SCRs in a string appears

- (B) Uneven voltage distribution of voltages across SCRs in a string appears

- (C) One of the SCRs shares maximum voltage and rest share same voltage in a string

- (D) Derating factor = 1-string efficiency

Key: **(A)**

Exp: Uniform distribution of voltages across SCR's is necessary so as to get the maximum string efficiency.

93. For a firing angle of 60° in respect of a single-phase half-wave controlled rectifier with resistive load supplied from a 230V (rms), 50 Hz supply, the average output voltage would be

(A) 52V

- (B) 77.5V

- (C) 104V

- (D) 155V

**Key:**

$V_{0(avg)} = \frac{V_m}{2\pi} (1 + \cos \alpha)$ Exp:  $=\frac{230\sqrt{2}}{2\pi}\left(1+\cos 60^{\circ}\right)=77.5V$

- 94. The frequency of ripple in the output voltage of a three phase controlled bridge rectifier depends on naineerina = Success

- (A) Firing angle

- (B) Load inductance (C) Load resistance (D) Supply frequency

Key: **(D)**

- 95. An SCR requires 50 mA gate current to switch it ON. The driver circuit supply voltage is 10V. The gate-cathode drop is about 1V. The resistive load supplied from a 100V dc supply

- (A)  $66\Omega$  A

- (B)  $73\Omega$

- (C)  $80\Omega$

- (D)  $100\Omega$

Kev:

Resistive load =  $\frac{(10-1-1)}{100 \times 10^{-3}} = 80 \Omega$ Exp:

- 96. Which is the important factor in the steady-state characteristics of a MOSFET?

- (A) Current gain

(B) Transconductance

(C) Output resistance

(D) Drain-source voltage

Kev: **(C)**

- 97. Consider the following statements about IGBT

- (A) It has high input impedance

- (B) It has low ON state voltage drop

- (C) Its switching speed is higher than that of the MOSFET

- (D) It is a voltage controlled device

Which of the above statements are correct?

- (A) 1, 2 and 3 only

- (B) 2, 3 and 4 only

- (C)1, 2 and 4 only (D) 1, 2, 3 and 4

Key: **(C)**

Advantage of GBT: Exp:

- 1. very low on state voltage drop.

- 2. Low driving power.

- 3. Easily controllable.

- 4. Superior current conduction capability.

## Drawbacks:

- 1. Switching speed is interior to that of a power MOSFET.

- 2. Possibility of latch up due to internal PNP thyristor structure.

- 98. When the drain voltage in an n-MOSFET is negative, it is operating in

- (A) Active region

- (B) Inactive region (C) Ohmic region (D) Reactive region

Key: **(B)**

- 99. The input power factor of the converter circuit may be defined as the ratio of

- (A) Total mean input power to the total rms input volt amperes

- (B) Total rms input volt amperes to the total mean input power

- (C) Total peak input volt amperes to the total rms input volt amperes

- (D) Total input rms volt amperes to the total input peak volt amperes

Key: **(A)**

I/P p.f is defined as the ratio of total mean input power to the total RMS input volt-amperes Exp:

$$p.f = \frac{E_{_{1}}I_{_{1}}\cos\varphi}{E_{_{ms}}I_{_{ms}}} = \frac{I_{_{1}}}{I_{_{ms}}}\cos\varphi$$

- In a single-phase full bridge inverter what is the advantage of a unipolar switching over the 100. bipolar switching?

- (A) Increase of the fundamental component by a factor of 1.15 for the same DC-input voltage

- (B) Elimination of 5<sup>th</sup> and 7<sup>th</sup> harmonics

- (C) Apparent doubling of the switching frequency

- (D) None of the above

Key: ( )

- 101. It is required to control the speed and braking operation of a dc shunt motor in both the directions of rotation. The most suitable power electronic circuit will be

- (A) A half-controlled converter

- (B) A fully-controlled converter

- (C) A diode-bridge converter

- (D) A dual converter

Key: **(D)**

- How can the 3<sup>rd</sup> harmonic current be filtered in Thyristor-controlled reactor? 102.

- (A) By connecting in delta

- (B) By connecting in star

- (C) By connecting in star-delta

- (D) none of the above

Key:

Exp: TCR connected in delta eliminates the third harmonic and its multiples.

- 103. For a 1-phase full-bridge inverter fed from 48V dc and connected to load resistance of 2.4Ω, the rms value of fundamental component of output voltage is

- (A) 20V

- (B) 21.6V

- (C) 34.4V

- (D) 43.2V

Key: **(D)**

Exp: R.M.S value of fundamental component of output voltage is

$$V_{i} = \frac{1}{\sqrt{2}} \frac{4V}{\pi} = \frac{1}{\sqrt{2}} \times \frac{4 \times 48}{\pi} = 43.2V$$

Engineering Success

- 104. A voltage source inverter is used when source and load inductances are respectively

- (A) Small and large (B) Large and small (C) Large and large

- (D) Small and small

Kev: **(A)**

IN VSI, dc source has small impedance. In VSI using thyristors, load commutation is possible Exp: only if load is under damped. For RLC load, the condition for the load to be under damped is

$$R < \sqrt{\frac{4L}{C}}$$

## **Directions:**

Each of the next sixteen (16) items consists of two statements, one labeled as the 'Statement (I)' and the other as 'Statement (II)'. Examine these two statements carefully and select the answers to these items using the codes given below:

## Codes:

- (a) Statement (I) and Statement (II) are individually true and statement (II) is the correct explanation of statement (II)

- (b) Statement (I) and Statement (II) are individually true but statement (II) is not the correct explanation of statement (I)

- (c) Statement (I) is true but statement (II) is false

- (d) Statement (I) is false but statement (II) is true

105. Statement (I): HVDC transmission is advantageous over HVAC for large power

transfer over long lines.

Statement (II): HVDC requires conversion equipment at two ends of the transmission

line.

**Key:** (B)

106. Statement (I): In the construction of a core-type power transformer, the high-voltage

winding is placed around the low-voltage winding in each limb.

Statement (II): When the high-voltage winding is placed around the low-voltage

winding in a core-type transformer, only one layer of high-voltage

insulation is required between the two coils.

**Key:** ( )

107. Statement (I): The magnetization curve of the actual power transformer is non-linear

and its effect is to introduce higher-order harmonics in the magnetizing

current.

Statement (II): The effect of the harmonic frequencies can be taken care of by

modifying the magnitudes of the phasors involved, and the phasordiagram at the fundamental frequency, with the assumption of a linear

magnetization, remains unaffected.

**Key: (B)**

108. Statement (I): The core-loss in a transformer is independent of the load current.

Statement (II): The core is made up of thin laminations interleaved at the joints to

avoid air-gaps.

Key: (A)

109. Statement (I): When the armature-iron of a dc machine rotates, it goes through the

influence of the north and the south poles, thus causing cyclic

variations of the linked magnetic flux and resulting in the occurrence

of hysteresis loss in the armature core.

Statement (II): The laminated armature construction limits the hysteresis loss to a

lower value.

**Kev:** (C)

110. Statement (I): Dampers are used in the alternators.

Statement (II): The voltage fluctuations are not reduced by the damper windings in an

alternator.

111. Statement (I): The rotor of an induction motor rotates in the direction of the rotating

magnetic field.

Statement (II): The rotor will start rotating in such a direction that it will oppose the

cause, i.e., the relative speed between the rotating field and stationary

rotor conductors should decrease.

Kev: **(A)**

112. Statement (I): The expression for the value of inductance L per conductor of an un-

symmetrically spaced 3-phase overhead transmission line contains an

imaginary term.

Statement (II): The presence of the imaginary term is due to the mutual inductance

between the phase conductors and can be eliminated by symmetrically

transposing the three line-conductors along the length of the line.

Key: ()

113. Statement (I): A large negative feedback is deliberately introduced in an amplifier to

make its gain independent of variation in parameters of active device

and other components.

A large negative feedback results in a high value of return difference Statement (II):

compared to unity which makes the feedback gain inversely,

proportional to feedback factor.

Key: **(A)**

114. Statement (I): An astable multivibrator is also called a free-running oscillator.

Statement (II): An astable multivibrator circuit forces an operational amplifier to

operate in the saturation region.

Key: **(A)**

115. Statement (I): An ideal op amp should have infinite band-width.

Statement (II): An ideal op amp should have infinite input resistance and zero output

resistance.

Key: **(B)**

116. Statement (I): Ready signal of microprocessor is used to detect whether a peripheral

is ready for the data transfer or not.

In the microprocessor during data transfer operations, the wait states Statement (II):

are added by forcing the ready signal low.

Key: **(A)**

READY signal should HIGH to increase delay. Exp:

**GATEFORUM**Engineering Success EE-Objective I

www.gateforum.com

117. Statement (I): The main difference between a micro-processor and a micro-controller

is that the former does not have any on chip memory.

Statement (II): A micro-processor does not need memory to run programmes.

**Key:** (C)

**Exp:** Microprocessor is having external memory which is required to store the program before

execution.

118. Statement (I): Frequency division multiplexing uses analog modulation systems.

Statement (II): Multiplexing helps transmitting a number of data simultaneously over

a single channel.

**Key: (B)**

119. Statement (I): A Gate Turn-Off is a pnpn device which can be turned on by a pulse of

positive gate current and turned off by a negative pulse.

Statement (II): A chopper is a static device which converts fixed dc input voltage to

variable dc output voltage.

**Key: (B)**

120. Statement (I): A switched-mode dc power supply has high efficiency and light

weight.

Statement (II): A switched mode power supply uses a dc to dc switching converter

switched at high frequency.

**Key:** (A)